关于Xilinx与modelsim的仿真联调,尤其是仿真环境的搭建,网上的信息都比较零散,我当初在联调的时候遇到比较多的问题,也是折腾了两天才弄好,下面的步骤我总结得非常详细,可以帮助大家少走弯路。

首先要做的是Xilinx仿真库的编译:

1、 Xilinx 仿真库编译

开始-》所有程序-》xilinx design tools-》simulation library compilation wizard。路径可能不同,只要找到simulation library compilation wizard并打开即可。

打开后选择相关的配置项: select simulator选择modelsim SE;我的电脑是32位,所以选择32位;simulator executable location中填入modelsim所在的路径,即安装目录下可执行文件modelsim.exe所在的路径,其它不用做修改,点击next。

选择语言,选择 Both VHDL and Verilog,点击next。

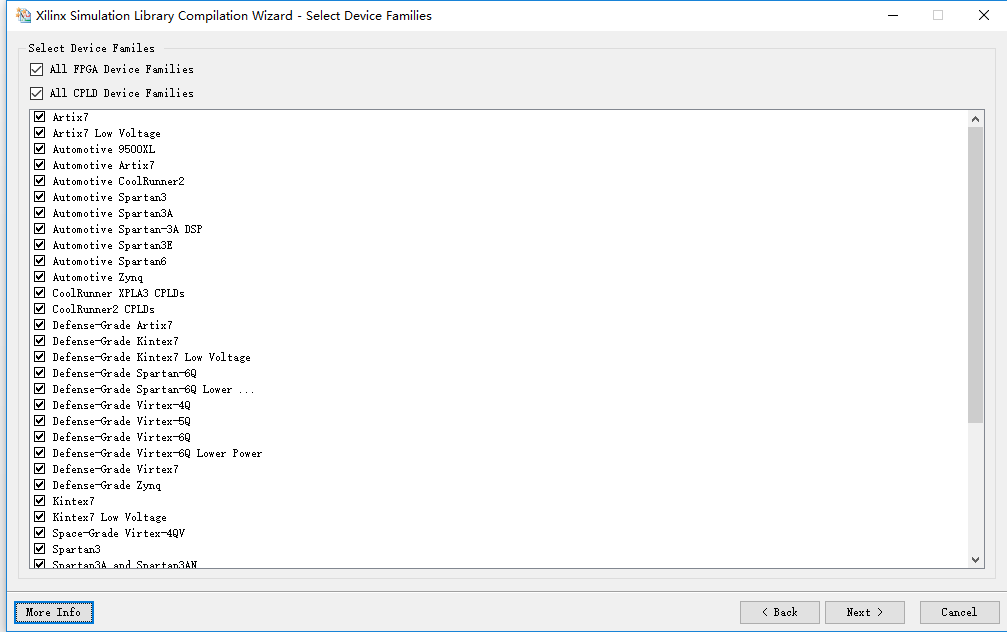

不做修改,选择全部器件,点击next。

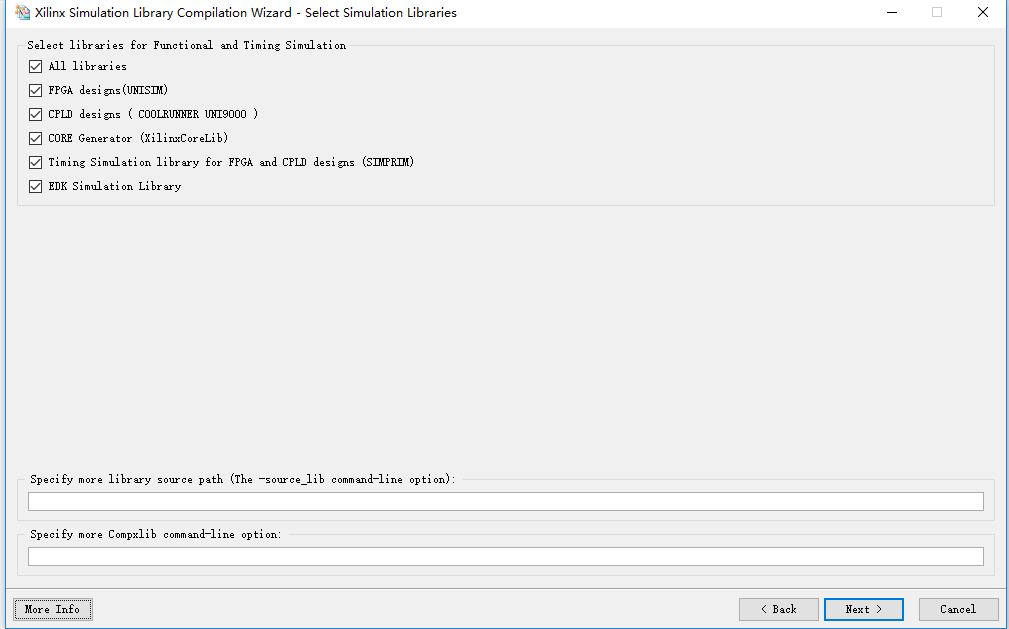

直接点击next。

根据安装实际情况,指定输出仿真库文件目录到EDK文件夹下,G:\Xilinx\14.7\ISE_DS\EDK,然后点击launch compile process自动生成仿真库

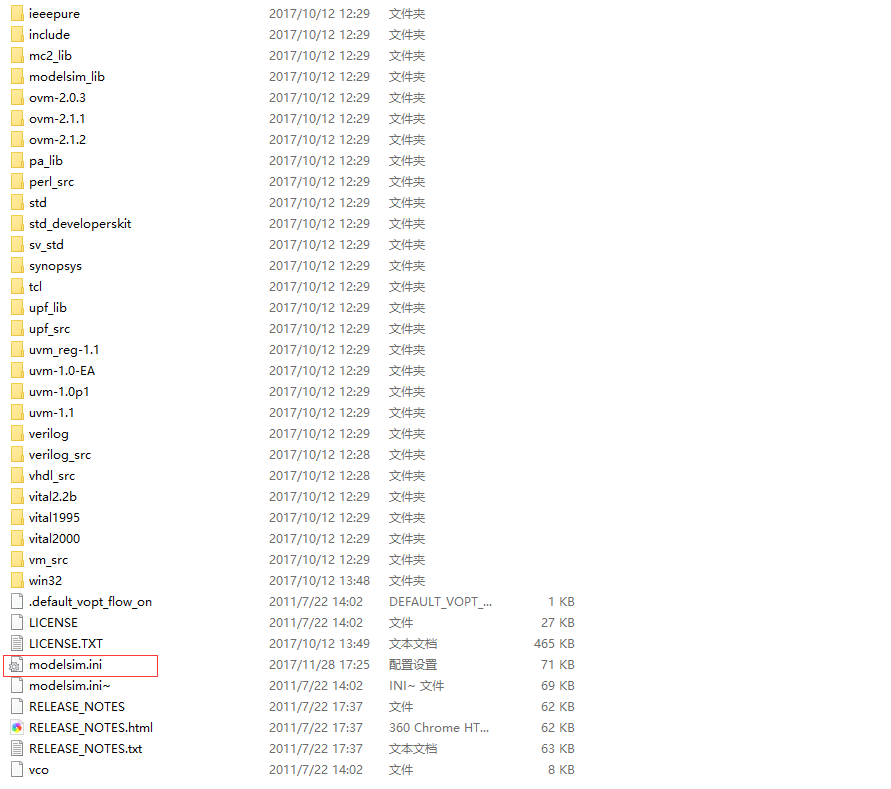

点击“Finish”,完成Xilinx 仿真库的编译,直接去输出仿真库的路径下可以找到modelsim.ini文件。

使用记事本或其他文本编辑器打开modelsim.ini文件,先找到这个library。

接着往后看,找到这段代码,这是modelsim仿真库的配置路径,复制这段代码

去到modelsim安装路径下,找到modelsim.ini文件。

使用记事本或其他文本编辑器打开modelsim.ini文件,找到其中的library项。

在后面粘贴前面复制的内容。

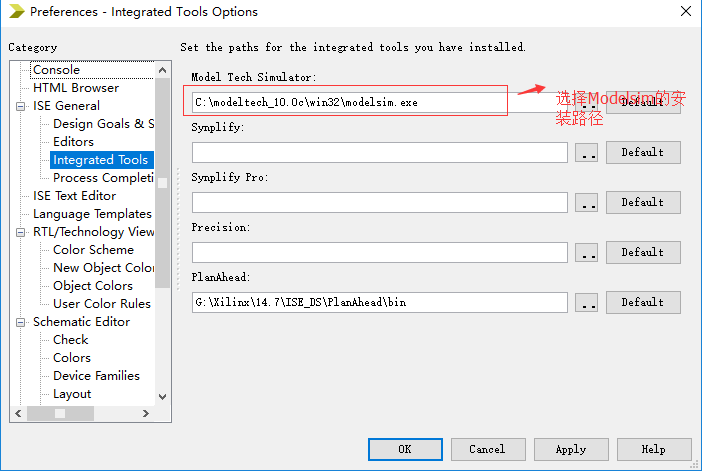

打开ISE软件,进行modelsim连接配置

打开edit-》preference -》integrated tools,model tech simulator 选择modelsim.exe所在路径。

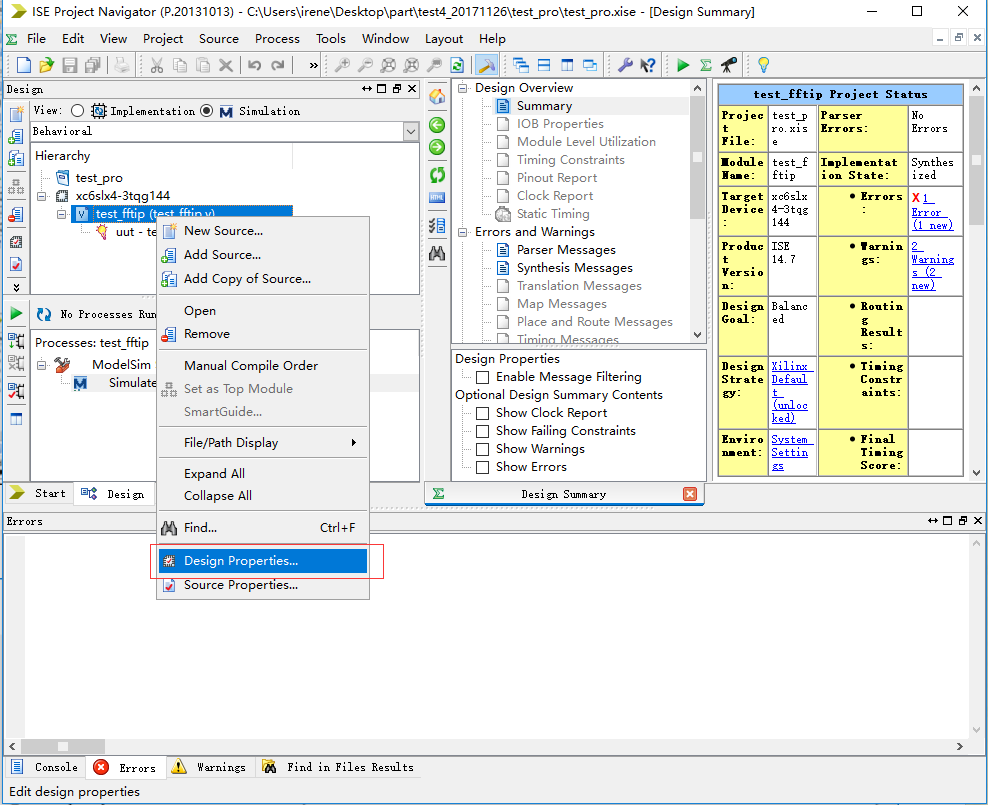

点击“design properties”

simulator选择modelsim-SE Verilog

点击“OK”,至此,Xilinx 仿真库编译完毕。

注意:转载请注明出处!